EziDebug������������Ѻã��м�Լ����������������ʽ��ʹ��ǰ����ʾ��FPGA�����������ϡ���������Ҫ���ܷ�Ϊ�Ĵ��������롢���ݲɼ��͵������ؽ�testbench������������֤���ĸ����֡�EziDebug֧��Altera��QuartusII����ƽ̨��ͬʱҲ֧��Xilinx��ISE���Ĵ������IJ������VHDL��Verilog HDLӲ���������ԣ���RTL��Ӳ�������ÿ���Ĵ�������һ�������Ĵ������ڴ��������½������ݲ����������ݵ���֮������������ʱ�Ĵ�������ֵ�ؽ�������FPGA���й������ڲ�����ʵ�źŲ��Ρ�������֤ͨ���Ƚ����������ж�Ӳ��������ȷ���

EziDebug ��һ������֧��FPGAӲ����֤�ĸ�����������ȫ���ӻ��Ƕ�֧��FPGA���̵ĵ��ԣ����ӵĵ��Թ��̣�ͨ���������ܺܿ���ҳ������еĴ��ӿ�Ӳ����֤�Ľ��ȡ�����������װ���㣬�����࣬������ݣ�ռ�õ�ϵͳ��Դ���٣���ʹ�õ����������У�ֻ��Ҫʹ�ò���ʮ���İ����ؼ�����������в�����

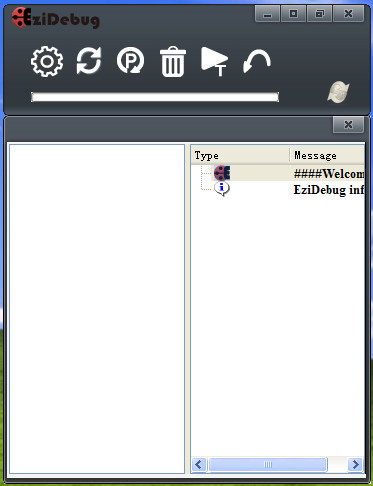

fpga��֤����lady(EziDebug )��ť����

˫��ͼ����û����Կ����������Ի�����ɵĽ��棬������Ľ��漴��Ҫ���������ͼ1��ʾ��������ťͼ��Ĺ������£�

1���������ã����ù��̵ľ���ѡ����磺���̵Ĺ���Ŀ¼��ɨ�����мĴ�����������������xilinx����altera�Ĺ��̵ȡ�

2��ȫ�����£�ȫ��ɨ�蹤���ļ���������ȡmodule�Ķ˿��źţ��Ĵ�����Ϣ�ȡ�

3�����ٸ��£����ָ��£���ֻɨ����¹����ļ��бȴ洢�����µ��ļ���

4��ɾ����������ɾ�������ļ����������ӵ�����Ϣ��

5������testbench����ѡ��������Ի�����Ҫ����signaltap�����ļ�������ѡ����ļ���Ӧ������Ȼ������testbench��

6��������һ��������ֻ�ָ���һ�β���ǰ���ı�ԭò����ע�⣺��֧�ֶ�γ�����

7��������ʾ�����û����˴���������������һ�ν��и��²����Ĵ��벻һ��ʱ������ʾ��

8����С�����ڰ�ť

9�����㴰�ڰ�ť

10������������ʾ�������л���ť

11���رմ��ڰ�ť

- PC�ٷ���

- ���ٷ��ֻ���

- IOS�ٷ��ֻ���

adams2020�����ƽ����Ѱ�

adams2020�����ƽ����Ѱ�

abaqus2022���İ�ٷ���

abaqus2022���İ�ٷ���

��������ʩ����־����(������)��Ѱ�

��������ʩ����־����(������)��Ѱ�

ͼ���������2.1.7 �ٷ���

ͼ���������2.1.7 �ٷ���

Tecplot 360 EX 2018 R1��Ѱ�

Tecplot 360 EX 2018 R1��Ѱ�

Altair HyperWorks 2019�����渽�ƽⲹ��

Altair HyperWorks 2019�����渽�ƽⲹ��

Altair Flux 2018��Ѱ渽�����

Altair Flux 2018��Ѱ渽�����

Altair Flux 2019��Ѱ渽�����

Altair Flux 2019��Ѱ渽�����

Altair Flux 2020 ��Ѱ渽��г����

Altair Flux 2020 ��Ѱ渽��г����

Vero VISI2021�ƽ��2021.0.2036��ɫ��Ѱ�

Vero VISI2021�ƽ��2021.0.2036��ɫ��Ѱ�

powermill ultimate�ƽ�棨�������룩2021���İ�

powermill ultimate�ƽ�棨�������룩2021���İ�

����Ӫ����2.1905.1�����

����Ӫ����2.1905.1�����

Meshmatic(�Ż�3Dģ��)1105�ٷ���

Meshmatic(�Ż�3Dģ��)1105�ٷ���

³���ʼ����1.0.0 �ٷ���

³���ʼ����1.0.0 �ٷ���

�����8.3.0.9�ٷ���

�����8.3.0.9�ٷ���

cjj�Mt 137-2020 �����������ճ����۱�PDF��Ѱ�

cjj�Mt 137-2020 �����������ճ����۱�PDF��Ѱ�

���繤��ʩ�����̺淶�°�pdf����������

���繤��ʩ�����̺淶�°�pdf����������

Ʒ��BIM5D����2.5.74.11868

Ʒ��BIM5D����2.5.74.11868

Ʒ��BIMģ�幤���������2.0.1 ���°�

Ʒ��BIMģ�幤���������2.0.1 ���°�

Ʒ��BIM��άʩ��������2.3.3 ���°�

Ʒ��BIM��άʩ��������2.3.3 ���°�

Ʒ��HiBIM����2.3.0 ��ʽ��

Ʒ��HiBIM����2.3.0 ��ʽ��

�������ƽ���2021��Ѱ�

�������ƽ���2021��Ѱ�

TracePro��ѧ��������8.1.0 ���°�

TracePro��ѧ��������8.1.0 ���°�

������۹�����1.1 ��ɫ��Ѱ�

������۹�����1.1 ��ɫ��Ѱ�

T20��������2020���°�v6.0 ��Ѱ�

T20��������2020���°�v6.0 ��Ѱ�

���߽�ģ��ʦ4.30�ٷ���ʽ��

���߽�ģ��ʦ4.30�ٷ���ʽ��

��Ԫ����(KYTool)3.7 ��Ѱ�

��Ԫ����(KYTool)3.7 ��Ѱ�

CAD�����װ(��װ�������)2018R8�ٷ����°�

CAD�����װ(��װ�������)2018R8�ٷ����°�

������BIM��װ����GQI20187.2.0.3068 64λ��

������BIM��װ����GQI20187.2.0.3068 64λ��

GB50106-2010T ������ˮ��ˮ��ͼ�����°�pdf������

GB50106-2010T ������ˮ��ˮ��ͼ�����°�pdf������

����������(CAD������)2018.06.19 ���°�

����������(CAD������)2018.06.19 ���°�

T20��������v3.0(֧��Autocad2016ƽ̨)���

T20��������v3.0(֧��Autocad2016ƽ̨)��� �Ҽ����������(��ѷ���װ����ά�������)

�Ҽ����������(��ѷ���װ����ά�������) 54 80����ת��(�������ת����γ�ȹ���)2.0

54 80����ת��(�������ת����γ�ȹ���)2.0 ���Ե������(JDPaint)5.19 ���İ�װ��(����

���Ե������(JDPaint)5.19 ���İ�װ��(���� ��ɵƽ������(������Ʋ������ݴ���ϵͳ)��

��ɵƽ������(������Ʋ������ݴ���ϵͳ)�� �ֲ�������������������Լ�����1.0 ��ɫ��

�ֲ�������������������Լ�����1.0 ��ɫ�� ����ѡ��ר��(������ҵ��Ա�ر�����)3.3 ��

����ѡ��ר��(������ҵ��Ա�ر�����)3.3 ��